Os artigos científicos de autoria de membros da comunidade brasileira de pesquisa em Materiais em destaque neste mês são:

Ambipolar Resistive Switching in an Ultrathin Surface-Supported Metal–Organic Framework Vertical Heterojunction. Luiz G. S. Albano, Tatiana P. Vello, Davi H. S. de Camargo, Ricardo M. L. da Silva, Antonio C. M. Padilha, Adalberto Fazzio, Carlos C. B. Bufon. Nano Lett. 2020, 20, 2, 1080-1088. https://doi.org/10.1021/acs.nanolett.9b04355

Edge-driven nanomembrane-based vertical organic transistors showing a multi-sensing capability. Ali Nawaz, Leandro Merces, Denise M. de Andrade, Davi H. S. de Camargo & Carlos C. Bof Bufon. Nature Communications volume 11, Article number: 841 (2020). Disponível em https://www.nature.com/articles/s41467-020-14661-x (acesso livre)

Microtubos de nanomembranas e materiais híbridos para dispositivos eletrônicos avançados

Alguns dos desafios das próximas gerações de smartphones, sensores e outros aparelhos eletrônicos podem ser resolvidos com a ajuda de microtubos de nanomembranas (folhas feitas a partir de vários materiais, condutores da eletricidade ou não, com espessuras nanométrica e dimensões laterais micrométricas, que podem se autoenrolar formando microtubos).

Na cidade de Campinas (SP), no Laboratório Nacional de Nanotecnologia do Centro Nacional de Pesquisa em Energia e Materiais (LNNano/CNPEM), um grupo de cientistas vem desenvolvendo expertise em processos de síntese, fabricação e caracterização de nanomembranas e suas aplicações. Em trabalhos que foram publicados em janeiro e fevereiro deste ano nos periódicos Nano Letters e Nature Communications, os autores exploram algumas potencialidades das nanomembranas, principalmente relacionadas à sua flexibilidade e dimensões, para desenvolver novos memoristores e transistores – dois dispositivos eletrônicos amplamente utilizados.

Mais precisamente, os pesquisadores do LNNano mostram que os microtubos de nanomembrana podem ser peças-chave na confecção de componentes promissores utilizando materiais orgânicos e híbridos (orgânico-inorgânico) como os memoristores e transistores. Dessa maneira, as novidades propostas nos artigos podem contribuir ao desenvolvimento de aparelhos e equipamentos ainda menores, flexíveis, portáveis, mais baratos e que combinem melhor desempenho e mais funcionalidades com baixo consumo de energia.

Em entrevista ao Boletim da SBPMat, Carlos Cesar Bof Bufon, autor correspondente dos dois artigos, fala sobre o impacto científico, tecnológico e social das pesquisas e sobre as competências e infraestrutura envolvidas na sua realização. Bufon é pesquisador e chefe da Divisão de Dispositivos do LNNano/CNPEM.

Boletim da SBPMat: – Os artigos apresentam avanços, desenvolvidos no LNNano, em tecnologias para dispositivos eletrônicos (transistores e memoristores). Na sua opinião, quais são as principais contribuições tecnológicas e/ ou científicas que estes artigos apresentam?

Carlos Cesar Bof Bufon: – O trabalho intitulado “Ambipolar Resistive Switching in an Ultrathin Surface-Supported Metal–Organic Framework Vertical Heterojunction” publicado na Nano Letters (doi: 10.1021/acs.nanolett.9b04355), reporta o desenvolvimento de um novo tipo de memoristor utilizando estruturas metal-orgânicas de superfície (SURMOFs). Os SURMOFs são estruturas híbridas compostas por íons metálicos conectados por ligantes orgânicos, altamente organizadas em superfícies recobertas com monocamadas quimicamente ativas (SAMs). Existem mais de 70 mil tipos de estruturas metal-orgânicas (MOFs) que podem ser preparadas como SURMOFs e que podem conferir novas funcionalidades a dispositivos eletrônicos. Além das novas funcionalidades, sua considerável flexibilidade mecânica e baixo custo despertam interesse na comunidade científica para aplicações. Porém, por se tratar de um material híbrido formando por elementos orgânicos e inorgânicos, a integração desta classe de materiais torna-se um desafio tecnológico. Com intuito de contornar essa limitação, este trabalho apresenta uma nova arquitetura para a integração dessas de estruturas SURMOFs e sua aplicação no desenvolvimento de um novo tipo de memoristor. A arquitetura proposta é baseada no contato elétrico superior de filmes ultrafinos de SURMOF HKUST-1 utilizando nanomembranas metálicas autoenroladas (microtubos). Os filmes de SURMOF explorados nesse trabalho apresentam espessuras da ordem de 20 nanômetros. Essa nova arquitetura abre caminhos promissores na área de dispositivos eletrônicos baseados em SURMOFs, bem como fornece uma plataforma tecnológica para a realização de estudos ainda não reportados na literatura para essa classe de materiais, como por exemplo, a investigação de como as cargas elétricas são conduzidas em camadas de SURMOFs ultrafinos.

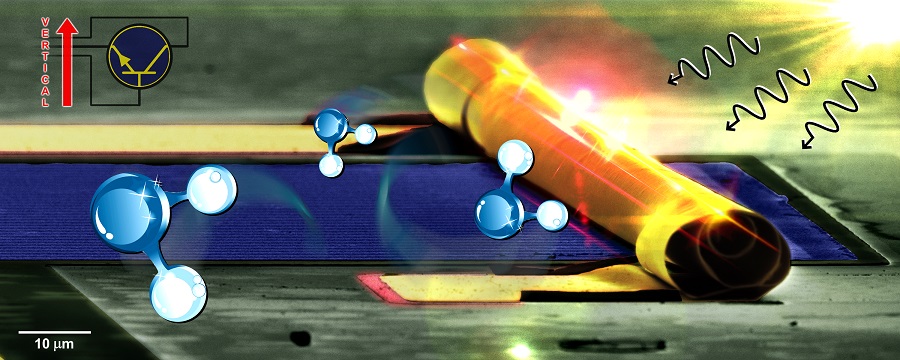

Já o trabalho intitulado “Edge-driven nanomembrane-based vertical organic transistors showing a multi-sensing capability” publicado na Nature Communications (doi: 10.1038/s41467-020-14661-x), apresenta o desenvolvimento de uma plataforma de transistor orgânico em arquitetura vertical. Os transistores são os principais componentes de circuitos e processadores eletrônicos. Comparados aos transistores inorgânicos, os transistores orgânicos têm como vantagens o baixo custo e sua fácil fabricação, que o tornam atraentes para dispositivos eletrônicos flexíveis em várias áreas. Uma grande vantagem dos transistores verticais está em sua fácil integração com dispositivos emissores de luz e fotodetectores na formação de sistemas optoeletrônicos integrados. Os dispositivos apresentados neste trabalho foram processados inteiramente por meio de técnicas convencionais de microfabricação e fotolitografia, o que é uma vantagem do ponto de vista da viabilidade tecnológica. Um grande diferencial destes novos transistores está relacionado à utilização de nanomembranas metálicas autoenroladas como eletrodos de dreno (um dos contatos do transistor), promovendo assim a formação de um contato mecânico suave com a camada de semicondutor orgânico. Nesta arquitetura, a camada semicondutora pode atingir espessuras menores que 50 nanômetros. Os dispositivos fabricados mostraram altas densidades de corrente (~0,5 A/cm2) com baixas tensões de operação (≤ 3 V). Com base em nosso estudo teórico, foi possível prever uma melhoria na estrutura do transistor, resultando em projeções de dispositivos com densidades de corrente de até 10 A/cm2. Tais valores – obtidos com baixas tensões de operação em uma plataforma composta por camadas orgânicas ativas – destacam o potencial desses dispositivos para futuramente serem integrados em aplicações eletrônicas flexíveis e portáteis. Além disso, os novos transistores mostraram-se capazes de detectar diferentes níveis de umidade e de luz, graças à plataforma de dispositivo baseada em nanomembranas autoenroladas. Portanto, os transistores desenvolvidos também possuem um grande potencial para o avanço da tecnologia de sensores da próxima geração.

Boletim da SBPMat: – De que maneira os resultados dos artigos poderiam impactar na vida cotidiana das pessoas (impacto social)? Você considera que as tecnologias propostas poderiam substituir as usadas atualmente ou criar novas aplicações? Se sim, quais seriam as vantagens destas novas tecnologias desenvolvidas no LNNano? Seria necessário dar muitos passos ainda para levar os resultados dos artigos ao mercado?

Carlos Cesar Bof Bufon: – O memoristor é considerado um dos quatro componentes eletrônicos fundamentais. Em um computador, é capaz de realizar as funções de processamento e de armazenamento de informação. Neste trabalho, o comportamento de memoristor foi observado em condições de alta umidade relativa (entre 90-70%). Análogo a uma espoja, as moléculas de água presentes no ambiente são absorvidas pelos nanoporos do SURMOF. Em determinado campo elétrico, essas moléculas facilitam a condução dos elétrons dentro do material através da alteração da sua resistência elétrica. A diferença na resistência elétrica pode chegar a 1 milhão de vezes utilizando baixas tensões de operação – menores que 2 V. Em uma aplicação prática, essa diferença pode corresponder a estados binários como 0 e 1. A total fabricação do dispositivo foi realizada com técnicas convencionais de fotolitografia, compatíveis com a produção em escala industrial. O fato de depender de umidade para seu funcionamento não limita sua aplicação comercial, pois isto pode ser facilmente contornado através de processos de encapsulamento, comuns na indústria de dispositivos eletrônicos.

Já a fabricação de transistores orgânicos em arquitetura vertical utilizando nanomembranas enroladas como eletrodos de dreno permite a redução da região de interesse para menos de 50 nanômetros (mais de mil vezes menor que a espessura de um fio de cabelo). Isso implica um avanço significativo na indústria eletrônica, porque a portabilidade de aplicações eletrônicas, como smartphones, computadores e televisores, depende da redução do número e do tamanho de transistores. O mecanismo de operação do dispositivo relatado neste trabalho amplia o entendimento atual sobre transistores orgânicos verticais, mostrando que as densidades de corrente podem ser melhoradas realizando-se manipulações cuidadosas na estrutura espacial do eletrodo metálico intermediário (fonte). Além disso, a preparação de microchips de transistores foi realizada com técnicas de microfabricação compatíveis com a escala industrial. Assim, esses dispositivos podem ser facilmente integrados em aplicações eletrônicas com algumas etapas adicionais, como o encapsulamento de microchips para evitar a degradação dos materiais orgânicos.

Os dois conceitos de dispositivos baseados em nanomembranas ampliam as possibilidades para o uso de materiais híbridos em eletrônica. Por mais que exista uma tendência para a substituição de uma tecnologia por outra, os conceitos desenvolvidos em nossos trabalhos buscam abrir novas fronteiras e possibilidades através o design de estruturas funcionais a partir de seus elementos fundamentais tais como átomos e moléculas.

Todas as tecnologias que desenvolvemos na área de dispositivos no LNNano/CNPEM estão firmemente calcadas tanto no entendimento dos conceitos fundamentais que governam as propriedades dos componentes como na aplicação tecnológica. Esses dois trabalhos foram iniciados fundamentalmente do zero. Em termos do seu nível de maturidade tecnológica (do inglês technology readiness level, TRL), os dispositivos alcançaram a validação funcional dos componentes em ambiente de laboratório (foi totalmente concluída). Dentro da escala TRL, atingimos o quarto nível de um total de 9, sendo este último a comercialização. Vale ainda ressaltar que o próximo nível a ser trabalhado precisa necessariamente envolver a participação do setor produtivo, que é, de fato, quem pode acelerar a chegada deste tipo de pesquisa ao mercado.

Boletim da SBPMat: – Conte-nos brevemente a história dos trabalhos reportados nos dois artigos: como e quando surgiu a ideia, se foi necessário reunir competências muito diversas, a infraestrutura utilizada, curiosidades etc.

Carlos Cesar Bof Bufon: – Os trabalhos são frutos de diferentes histórias, mas foram desenvolvidos no mesmo grupo de pesquisa com a ideia comum de explorar as potencialidades das nanomembranas na área de dispositivos funcionais. Esta temática faz parte do meu projeto Jovem Pesquisador financiado em 2016 pela FAPESP. A ideia da aplicação dos SURMOFs como memoristor, utilizando como contato superior as nanomembranas, foi desenvolvida em conjunto com o pós-doutorando Dr. Luiz Gustavo Simão Albano. O nosso grupo de pesquisa começou a avaliar a viabilidade tecnológica de utilizar os SURMOFs como materiais funcionais em dispositivos há cerca de 3 anos. Desde então, o grupo vem estabelecendo de forma continuada a implementação das rotas de síntese e integração para aplicações na área de componentes eletrônicos.

O trabalho foi realizado inteiramente no LNNano/CNPEM, e conta com uma lista de coautores que contribuíram ativamente para tornar possível a realização deste trabalho: Tatiana P. Vello (crescimento dos SURMOFs), Davi H. S. de Camargo (fabricação de dispositivos e ilustrações), Ricardo M. L. da Silva (fabricação de dispositivos), Dr. Antonio C. M. Padilha (simulações DFT) e Prof. Dr. Adalberto Fazzio (simulações DFT).

O trabalho com o transistor também segue o padrão do memoristor – combinação de materiais funcionais e nanomembranas. Há cerca de 15 anos comecei a me interessar pelas potencialidades do uso de camadas nanoestruturadas como blocos fundamentais em uma eletrônica vertical. Ao tomar conhecimento dos trabalhos do Prof. Ivo Hümmelgen, da UFPR (falecido em 2018), na área de transistores verticais, uma série de vantagens e desafios me chamaram a atenção. A ideia do trabalho surgiu ao antecipar que a melhoria no desempenho do dispositivo poderia ser alcançada com o uso de um eletrodo de dreno baseado em nanomembrana enrolada e um eletrodo intermediário (fonte) padronizado usando fotolitografia. Em maio de 2018, o Dr. Ali Nawaz (ex-aluno do Prof. Ivo!), natural do Paquistão, iniciou a execução do projeto no LNNano/CNPEM. Sendo um projeto de execução complexa, as infraestruturas avançadas para processamento e caracterização de dispositivos do LNNano/CNPEM foram fundamentais. E da mesma forma que o memoristor, a pesquisa dependeu de um conjunto de expertises variadas. Durante o projeto, o Dr. Leandro Merces prestou assistência crítica na investigação dos aspectos teóricos dos dispositivos, enquanto os colaboradores Davi Camargo (especialista em microfabricação) e Denise de Andrade (estagiária de graduação pela Universidade Estadual de Ponta Grossa), forneceram ao trabalho todo o suporte técnico necessário.